# Wisconsin Electric Machines and Power Electronics Consortium

# RESEARCH REPORT

Current Peak Limiting for a Series Resonant DC Link Power Conversion Using a Saturable Core

Y. Murai, S.G. Abeyratne

Dept. of Elec. and Comp. Engr.

Gifu University

1-1 Yanagido, Gifu

Gifu 501-11

Japan

T. A. Lipo, P. Caldeira

Dept. of Elec. and Comp. Engr.

University of Wisconsin-Madison

1415 Johnson Drive

Madison, WI 53706

Department of Electrical and Computer Engineering 1415 Johnson Drive Madison, Wisconsin 53706

© June 1991 Confidential

# CURRENT PEAK LIMITING FOR A SERIES RESONANT DC LINK POWER CONVERSION USING A SATURABLE CORE

Y. Murai and S. G. Abeyratne

Dept. of Electronics & Computer Engng., Gifu University, 1-1 Yanagido, Gifu, Gifu 501-11, Japan

T. A. Lipo and P. Caldeira

Dept. of Electrical & Computer Engng., University of Wisconsin-Madison, 1415 Johnson Drive, Madison, WI 53706, U.S.A.

Abstract. High frequency resonant dc link power conversion circuits often experience irregular high peak current pulses during three phase operation and the pulses rise to over twice the regular pulse amplitude giving rise to current or voltage fluctuations at the output side. This high peak current/voltage problem appears to be common to both series/parallel resonant types respectively because of duality of the systems. In this paper current peak limiting has been performed by means of a saturable core inserted in the DC link as the resonant inductance. A simplified circuit limiting peak current is proposed and the resulting performance of the system is investigated by digital simulation.

Keywords. Series resonant de link, Resonant link converter, Zero current switching, High density power conversion.

#### INTRODUCTION

Power conversion schemes with an ac or dc resonant link, featuring zero voltage or zero current switching have expanded enormously recently. The method involves the possibility of having not only very low switching losses but also a higher power density. In a previous paper several of the authors proposed a series resonant dc link type ac to ac power conversion scheme [1]. This converter is the dual of the parallel resonant dc link type and the switching occurs at zero current instants. In addition, the system utilizes only twelve thyristors for full double bridges at the input and at the output. Thus it features a minimum number of devices as well as high current and high voltage withstand margins because of the use of thyristors.

However, this system experiences very high peak currents depending upon the voltage difference when the conducting phase changes. The pulse amplitude occasionally becomes two or three times larger than that of the normal pulse height and disturbs the output current as well as the voltage regulation. In the case of the parallel resonant de link converter, the problem encountered is not the occurrence of high current peaks but high voltage peaks that arise when the switching of conducting transistors occurs between phases. This situation is expected since the two schemes are duals of each other. A method of voltage clipping for that system was presented by utilizing an extra transistor, diode and a capacitor [2].

It is shown in this paper, that to realize current clipping, a simple saturable ferrite core can be employed in place of the resonant inductance. The principles of the pulse limiting and the simplification of the circuit are explained in detail and the control strategies adopted are discussed. A new method for establishing the switching function and a feed back method for selecting the optimum biasing current, are also presented. Since the trimming or circulating current mode is not used, this system allows a simple control method for operation while still maintaining stability accompanied by good motor torque characteristics.

#### PRINCIPLE OF OPERATION

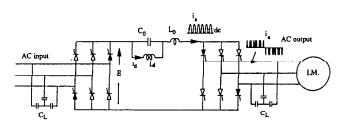

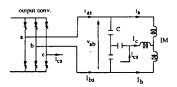

Prototype System Figure 1 shows a prototype of a series resonant dc link converter. The inductance  $L_0$  and the capacitance  $C_0$  form the high frequency series

resonant circuit and the capacitor banks at the output and input are simple low-pass filters needed to maintain the resonant frequency and to obtain better output and input current waveforms. The resonating current  $\mathbf{i}_s$  is shown in the figure. The dc current  $\mathbf{I}_d$  is superimposed on the resonant current by the inductance  $L_d$  which is very large and is considered as a constant current source.

The resonating current  $i_s$  begins by triggering the four thyristors shown in black. After the occurrence of each current pulse, all the thyristors are extinguished and bias current  $I_d$  begins charging the resonant capacitor  $C_0$  linearly so that the forward bias is reached for the next pair of thyristors to be triggered. When the forward bias has reached a settled threshold voltage, the next set of four thyristors are triggered to obtain a new current pulse.

The switching of main thyristors is done only at zero current instants of is resulting in very low switching losses. The current pulses are distributed to each phase by the method of Pulse Density Modulation (PDM)[1].

Resonant Pulses

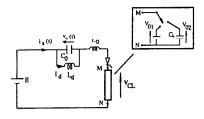

A mono-phase equivalent circuit of the three phase converter topology is shown in Fig. 2 (a). The voltage E is the output voltage of the input converter and  $V_{CL}$  is the line line voltage of the output capacitor bank. The capacitor  $C_L$  represents the effective lumped capacitance of the filter capacitors at the input and output bridges. Thyristor  $T_h$  represents the effect of the conducting four thyristors in series and the selector switch shows the possibility of selecting different output phases.

Due to the fact that the inductance  $L_d$  is sufficiently large, the DC offset given by the current  $I_d$  is almost constant. Since the output frequency is low compared with the resonant frequency and the capacitor  $C_L$  is also relatively large, the voltage  $V_{CL}$  across the capacitor  $C_L$  can be assumed constant over the period of each current pulse. Under these assumptions, the circuit equation is simplified as,

E -

$$V_{CL} = L_0 \frac{di_s}{dt} + \frac{1}{C_0} \int (i_s - I_d) dt$$

(1)

and the resulting current is becomes

$$i_{s} = I_{d} (1 - \cos \omega_{0}t) + \sqrt{\frac{C_{0}}{L_{0}}} V_{th} \sin \omega_{0}t$$

where,

$$\omega_{0} = \sqrt{\frac{1}{L_{0}C_{0}}}$$

(2)

$V_{th} = E - V_0 - V_{CL}$ ;  $V_0$ : initial voltage across  $C_0$ .

Fig. 1. Conventional high frequency series resonant DC link ac/ac converter.

(2')

Therefore, the peak value of  $i_s$  is dominated by the DC off-set  $I_d$  and the threshold voltage  $V_{th}$ . From equation (2), the maximum current  $I_{smax}$  can be expressed as

$$I_{smax} = I_d + \sqrt{I_d^2 + \frac{C_0}{L_0} V_{th}^2}$$

(3)

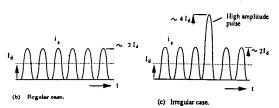

Therefore  $I_{smax}$  becomes constant provided that  $V_{th}$  and  $I_d$  are kept constant as shown in Fig. 2 (b).

Irregular Current Peaks

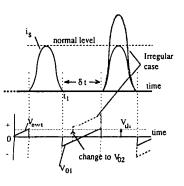

When the output thyristors are switched between different output phases, triggering at  $V_{th}$  is not always available. As a result, irregular current peaks appear as shown in Fig. 2 (c). In Fig. 2 (a), if the thyristor  $T_h$  stops conducting at time  $t_1$ , the following equations are possible with reference to the circuit in Fig. 2 (a).

$$E - \left(V_{C0} + L_0 \frac{d\{i_s(t)\}}{dt}\right)_{t=t_1} - V_{01} - 0$$

(4)

where the phase selected has an output voltage of  $V_{01}$ . As the capacitor voltage  $V_{C0}$  does not change instantaneously, the voltage of inductance  $L_0$  just before  $t_1$  moves to the voltage  $V_{swt}$  across thyristor  $T_h$  at the moment just after  $t_1$ ; that is,

$$(V_{swt})_{t=t_1^+} = \left(L_0 \frac{d[i_s(t)]}{dt}\right)_{t=t_1^-}$$

$$= E - (V_{C0})_{t=t_1^-} - V_{01}.$$

(5)

#### (a) Simplified mono-phase model

(d) V<sub>swt</sub> and i<sub>S</sub>.

Fig. 2. Current pulse peak at conventional system

When thyristors stop conducting at time  $t_1$ , the calculation for selecting the next mode is accomplished during the interval given by  $\delta t$  and the capacitor charges up linearly by the constant biasing current  $I_d$ . The voltage  $V_{shv}$  goes up to  $V_{th}$  where the next triggering is scheduled as shown in Fig. 2 (d);

$$(V_{swt})_{t=t_1+\delta t} = V_{th}$$

$$= (V_{swt})_{t=t_1^*} + I_d \frac{\delta t}{C_0}$$

$$= E - (V_{C0})_{t=t_1} - V_{01} .$$

(6)

However, when  $V_{02}$  is selected for the next current pulse,  $V_{swt}$  changes to

$$(V_{swt})_{t=t+\delta t} = E - (V_{C0})_{t=t_1} - V_{02}$$

(7)

This case is equivalent to the case where the selector switches move from  $V_{01}$  to  $V_{02}$  in Fig. 2 (a) during the period  $t_1 < t < t_1 + \delta t$ . If the voltage  $V_{02}$  is much larger than  $V_{01}$ .  $V_{swt}$  at  $t=t+\delta t$  rises far beyond  $V_{th}$  and a high peak current pulse results as shown in dotted line in Fig. 2 (d). As a result the system becomes disturbed. Since the biasing current  $I_d$  varies because of finite inductance  $L_d$ ,  $I_d$  control, carried out by switching the input thyristors to other input phase voltages according to the error  $\epsilon$  in  $I_d$  (=  $I_{dref}$  -  $I_d$ ), is difficult. Since the voltage E also changes, it exaggerates the above phenomena.

#### CURRENT PEAK LIMITING

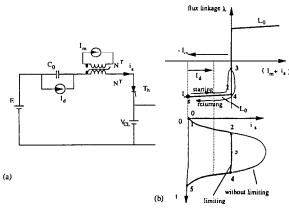

Current peak limiting is proposed to eliminate undesirable high pulses from occurring and to assure uniform pulse height. Figure 3 illustrates the basic idea of current peak limiting. The system shown in Fig. 3(a) illustrates a simplified mono-phase equivalent circuit for current peak limiting. In this circuit, the resonant inductance  $L_0$  is replaced by a saturable inductance with a biasing current  $I_m$  and the dc inductance  $L_d$  is expressed by a constant current source  $I_d$ .

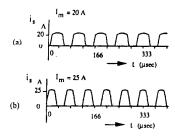

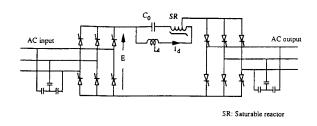

The principle of the current pulse limiting is illustrated in Fig. 3(b). In the characteristic of the saturable reactor, i.e., existing current  $i_s + I_m$  vs. magnetic flux linkage  $\lambda$ , the current  $I_m$  biases the core in the negative direction. The gradient of the slope in the saturated region is equal to the resonant inductance. Lo and the non-saturated region offers a very high inductance. In the circuit in Figure 3(a), when the thyristor  $T_h$  is triggered the current pulse starts flowing and the flux  $\lambda$  begins to increase toward point 2 and then to 3 and the current reaches almost a plateau, suppressed by the high inductance and returns to zero passing through points 3, 4 and 5 in that order and the corresponding current wave becomes as shown in Figs. 4(a) and (b). Figure 5 shows the actual three phase configuration with current peak limitine.

Fig. 3. Illustration for the principle of current pulse limiting.

Fig. 4. Examples of current pulses i<sub>s</sub> for the circuit with saturable core.

Fig. 5. Actual circuit configuration with current peak limiting.

In this system the biasing current is simply fed from the inductor  $L_d$  and the biasing current automatically changes according to the load current.

# CONTROL SCHEME

Output Converter Control

In this scheme the output voltage of the converter has been defined and the actual output voltage is compared with the reference voltage to generate a switching function. In the implementation of the scheme, the output reference voltages are modified from pulse to pulse by which means the voltage feedback is indirectly achieved.

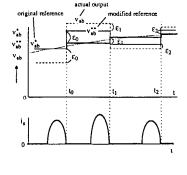

The output voltage feedback criterion is illustrated in Fig. 6. For example, let  $v_{ab}^*$  and  $v_{ab}^{**}$  represent the defined reference and the modified reference, respectively. When the deviation  $\epsilon_0 = v_{ab}^* \cdot v_{ab}$  exists at  $t = t_0^*$ , the modified reference during  $t_0 < t < t_1$  is set as  $v_{ab}^{**} = v_{ab}^* + \epsilon_0$ , then the required charge to boost up the next average voltage  $v_{ab}$  to the reference  $v_{ab}^{**}$  is performed. After this procedure, if the deviation  $\epsilon_1 = v_{ab}^{**} \cdot v_{ab}$  results at  $t = t_1^*$  the deviation  $\epsilon_1$  will be used for the next modified reference as  $v_{ab}^{**} = v_{ab}^* + \epsilon_1$  as illustrated in the figure. This method is also particularly effective in reducing the torque ripples of induction motor drives.

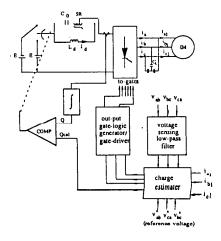

The overall system diagram is given in Fig. 7. Thyristor selection for triggering is performed based on the sign of the charge demand by each phase and the estimation of charges required is done in such a manner that the errors sustained in the output voltage are canceled out with the estimated charges. A detailed derivation of charges required to correct voltage errors at the output is given in the Appendix.

Since the required charges  $\Delta q_{uv}$ ,  $\Delta q_{bv}$ , and  $\Delta q_{cv}$  follow the relation  $\Delta q_{uv} + \Delta q_{bv} + \Delta q_{cv} = 0$  in eq. (11), three thyristors can be uniquely defined as shown in Table 1. For a particular "MODE" in Table 1, there appear two charge quantities with the same sign as shown in Table 2. Two thyristors in the output bridge are selected for firing at a time. Therefore, having decided the mode, the two thyristors to be fired next, are selected. For this purpose, the comparison between the

(definition of voltages and currents)

Fig. 6. Output voltage control.

- : Positive charge

- : Negative charge

Table 1. Polarity combinations of required charges.

+ : Upper thyristor

- : Lower Thyristor

Table 2. Combinations of triggering thyristors for the modes of Table 1.

Fig. 7. Overall control diagram.

magnitude of required charges is done. The phase thyristors with positive maximum and negative maximum required charges are

The relevant columns in Table 1 to which the selected charge belongs gives the two lines to be selected. Positive signs in Table 1 indicate the thyristors with a positive sign (top three thyristors) and the negative signs indicate the thyristors with the negative sign. Accordingly, the thyristors shown in black in Fig. 1 and Fig. 5 represent Mode 1 and it follows from Table 2 that at this instant  $\Delta q_a$ is larger than ∆qb.

Input Converter Control

The input converter involves Id control with reference Idrof which is determined by the required charges. Hence, this system uses a current feedback loop from the output to the input converter in addition to the voltage feedback used in the control of output converter. As the load increases, system needs a larger Id for the energy balance.

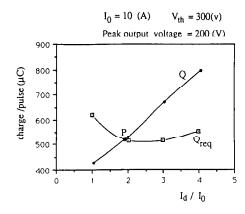

In the implementation of the system, I<sub>d</sub> adjustment can be achieved by a simple feedback criterion that uses comparison of charges. It should be noted that if the thyristor threshold voltage Vth is defined, then the charge Q afforded by a single current pulse is roughly calculated by the bias current Id. Therefore, to maintain an energy balance between input and output, an adequate Id should be selected to balance the required charge Qreq. Fig. 8 shows the tendencies of Q and Qreq according to biasing current Id which is normalized by the amplitude Io of output motor current.

To the left of the balancing point P in Fig. 8, the possible charge Q is less than the required value  $Q_{req}$ , in which case Q is not sufficient to correct the errors and the motor currents are not smooth. When  $I_d$  is increased beyond the balance point, the system has a higher capability of correcting errors but the ripple in the output voltage increases. Hence, Id control should be implemented so as to balance Q with Qreq, i.e.,  $I_d / I_0 = 2$ . Therefore, the thyristors in the input converter should be switched to have the polarity of the output voltage E as,

- (i) If  $Q > Q_{req}$ , input DC voltage is switched to +E to increase  $I_{def}$ .

- (ii) If Q <  $Q_{req}$ , input DC voltage is switched to -E to decrease  $I_{dref}$ .

The voltage E depends on the input three phase voltages and the selection of triggering phases is performed as the same manner as in [3] to have simultaneous unity power factor and sinusoidal input

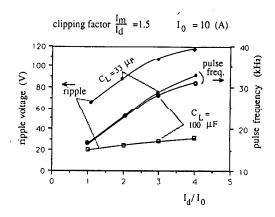

Other Calculated Results Figure 9 shows the tendency of the pulse frequency and the ripple voltage in the output. In this figure, when  $I_d$  increases, the pulse frequency increases because of less &t [the interval between pulses in Fig. 2 (d)] and the output ripple voltage  $V_{\text{ripple}}$  increases because of the increased supply of charge. It also shows that the larger filter capacitor  $C_L$  causes smaller voltage ripple in the output. In Fig. 8, it is demonstrated that as  $\delta t$  decreases according to the increase of  $I_d$ , the required per-pulse-charge  $Q_{req}$  with constant output current  $1_0$  also decreases before the balancing point P, whereas the charge  $Q_{req}$  again increases after P because of excessive regulation by an excessive supply of charge.

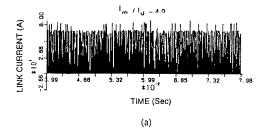

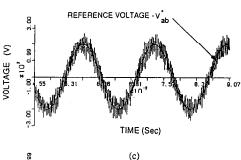

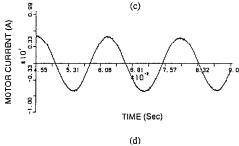

Figure 10 shows dependencies of the peak voltage stresses across the resonant capacitor and across the thyristors. The figure also shows that Viipple depends on the increase of capacitor CL. According to the increase of CL, smoother motor current and less voltage stresses on resonant elements and switches clearly result. In Fig. 11, simulated waveforms are shown. In Fig. 11 (a), pulses are shown with very small amplitude fluctuation compared with that of the previous prototype system [1]. Figure 11 (c) and (d) show the output voltage and current. Both are clearly well regulated and have sinusoidal waveform.

# CONCLUSION

In this paper, a new current-peak limiting scheme was proposed by utilizing a simple saturable ferrite core in place of the resonant inductance. The principles of the pulse limiting and the simplification of the circuit were performed and the control strategies adopted have been discussed. A new method for establishing the switching function and a feed back method for selecting optimum biasing current, have also been presented. Although a trimming procedure or circulating mode is not used, this system provides stable and good ent regulation in straightforward, simple manner

Fig. 8. Dependencies of Qcal and Q upon Id.

Fig. 9. Dependencies of ripple voltage and pulse frequency upon Id.

$I_d = 20 \text{ (A)} \quad I_0 = 6 \text{ (A)} \quad V_{th} = 300 \text{ (V)}$

FILTER CAPACITANCE - C, (LF)

200

300

Fig. 10. Voltage stresses.

100

ε

STRESS

VOLTAGE

PEAK

600

400

#### REFERENCES

[1] Y. Murai and T. A. Lipo, "High Frequency Series Resonant DC Link Power Conversion," IEEE-IAS Conference Record, 1988, pp. 648-656

pp., 648-656.

[2] D. M. Divan," The Resonant DC Link Converter--A New Concept in Static Power Conversion," IEEE-IAS Conference Record, 1986, pp. 648-656.

pp. 648-656.

[3] P. Caldeira, K. W. Marschke, M. T. Aydemir, T. A. Lipo and Y. Murai," Utilization of the Series Resonant DC Link as a DC Motor Drive," IEEE-IAS Conference Record, 1990, pp. 813-819.

### APPENDIX

# Required Charges

As shown in Fig. 6, assuming average currents to flow in all phases simultaneously,

$$\mathbf{I}_{\mathtt{as}} + \mathbf{I}_{\mathtt{bs}} + \mathbf{I}_{\mathtt{cs}} = 0$$

$$\Delta V_{ab} = (I_{as} - I_{a} - I_{ba} + I_{b}) \Delta t / C_{L}$$

$$\Delta V_{cb} = (-I_{bs} + I_b + I_{cs} - I_c) \Delta t / C_L$$

$$\Delta V_{ac} = (-I_{cs} + I_{c} + I_{as} - I_{a}) \Delta t / C_{L}$$

(8)

Defining,

$$\begin{split} I_{a} & \Delta t = \Delta q_{a} \\ I_{a} & \Delta t = \Delta q_{a} \\ \Delta V_{ab} C_{L} = \Delta q_{ab} \end{split} \tag{9}$$

(similar notations were adopted for other phases)

Substituting (9) into (8) and solving for  $\Delta q_{as}, \Delta q_{bs}, \Delta q_{cs}$  the following equations are derived.

$$\Delta q_{as} = (\Delta q_{ab} + \Delta q_{sc} \cdot \Delta q_b - \Delta q_c + 2 \Delta q_s) / 3$$

$$\Delta q_{bs} = (-\Delta q_{ab} - \Delta q_{cb} - \Delta q_c - \Delta q_c \cdot 2 \Delta q_b) / 3$$

$$\Delta q_{cs} = (\Delta q_{cb} - \Delta q_{ac} + 2 \Delta q_c - \Delta q_s - \Delta q_b) / 3$$

(10)

Equation (10) indicates that

$$\Delta q_{xx} + \Delta q_{xx} + \Delta q_{cx} = 0 \tag{11}$$

and the triggering thyristors can be uniquely defined as shown in the

Fig. 11 Simulated waveforms.