### Research Report

96-13

### A Matrix Converter Using Reverse Blocking NPT-IGBT's and Optimized Pulse Patterns

S. Bernet, T. Matsuo, T.A. Lipo

Wisconsin Power Electronics Research Center University of Wisconsin-Madison Madison WI 53706-1691

Wisconsin

**E**lectric

Machines &

Power

**E**lectronics

Consortium

University of Wisconsin-Madison College of Engineering Wisconsin Power Electronics Research Center 2559D Engineering Hall 1415 Engineering Drive Madison WI 53706-1691

© June 1996 - Confidential

# A Matrix Converter Using Reverse Blocking NPT-IGBT's and Optimized Pulse Patterns

Steffen Bernet, Takayoshi Matsuo and Thomas A. Lipo

University of Wisconsin-Madison Electrical and Computer Engineering 1415 Engineering Drive Madison, Wisconsin 53706

Abstract—The paper compares three-phase to three-phase IGBT matrix converters in which the required four-quadrant switches are realized by conventional common collector configurations and reverse blocking NPT-IGBT's respectively. A sophisticated semiconductor loss model is used to compute the converter losses for both switch configurations. New pulse patterns are derived to minimize the input current harmonics.

### I. INTRODUCTION

In recent years the three-phase to three-phase matrix converter (MC) has received considerable attention as an alternative to hard and soft switching dc-link converters. The topology was first investigated in 1976 [1] and then more recently by Venturini [2], [3]. Reference [3] proposes a scheme which generates sinusoidal input currents at unity power factor and increases the voltage transfer ratio to the maximum possible value of q=v<sub>1</sub>/v<sub>0</sub>=0.866. Since then various control principles including space vector modulation (e.g. [4], [5], [6]), and optimized pulse patterns (e.g. [7]) have been proposed overcoming most of the limitations of the matrix converter.

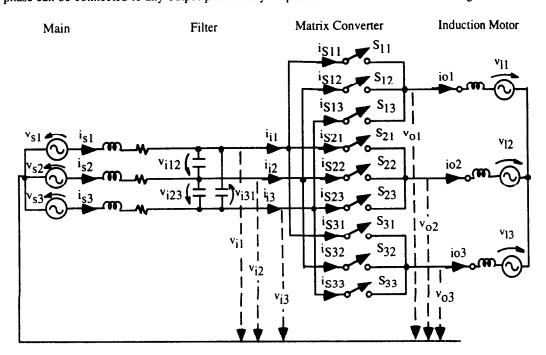

Nine four-quadrant switches (4QSW's) are arranged so that any input phase can be connected to any output phase at any

time (Fig. 1). Since the MC operates between a voltage source and a current source there must be always exactly one switch in each of the three switch groups (s1j/ s2j/ s3j; j=1,2,3) closed to avoid short circuits at the input and open phases at the output.

The MC topology has some distinct advantages over conventional hard switching PWM-rectifier /dc-link/ inverter structures. For example the MC does not require a dc-link capacitor due to its single stage power conversion. Furthermore it is expected that the MC generates substantially less switching and total losses than the comparable dc-voltage link topology, because the average commutation voltage of the MC (line-to-line-voltage) is distinctly lower than that of the dc-link topology (dc-linkvoltage). On the other hand the dc-link converter requires only 24 semiconductors (12 IGBTs, 12 diodes) and the MC needs 36 semiconductors (18 IGBTs, 18 diodes) if conventional IGBT's in a common emitter or common collector configuration are applied (Table I). However, the use of forward and reverse blocking NPT-IGBT's reduces the number of semiconductors in the MC by 50% bringing the converter in a real competitive position to the well known dclink topology.

The paper presents a description of the stress of the fourquadrant switches of a hard switching MC for conventional

Fig. 1: Circuit configuration of a three-phase MC

common collector switch configurations (CCC's) and switch implementations with reverse blocking NPT-IGBT's (RB-NPT-IGBT's). The switching and on-state losses of both switch implementations are measured in a suitable test circuit. The results achieved are the basis for an estimation of the total converter losses using a new power semiconductor loss model. Optimized pulse patterns which considerably reduce the input current harmonics are proposed.

### II. FUNDAMENTAL COMMUTATIONS OF A MATRIX CONVERTER

The commutation of an output phase current from one switch to another in each of the three switch groups can be described by the equivalent commutation circuit presented in [8]. In this case the load current corresponds to the motor phase current under consideration, the commutation voltage represents the effective line-to-line voltage at the input and the minimum values of the commutation inductivity and the commutation capacity are given by the stray inductance of the circuit and the output capacitance of the semiconductors respectively. Corresponding to the power of the load, two fundamental types of commutations can be distinguished - the so called inductive commutation and the capacitive commutation [8]. The inductive commutation is initiated by a hard turn-on transient of a 4QSW (IGBT) and completed by the passive turn-off transient during the interruption of the reverse current. In contrast to this the capacitive commutation is characterized by a hard turn-off transient (IGBT) and a low loss passive zero voltage turn-on transient.

Because both the commutation voltage (line-to-line input phase voltage) and the load current (motor phase current) change the polarity during the operation of the matrix converter the switches in Fig. 1 must be forward and reverse blocking bi-directional current conducting switches (4QSW's).

#### III. PRACTICAL IMPLEMENTATIONS OF FOUR-QUADRANT SWITCHES ON THE BASIS OF IGBTS

The switches of a MC should be realized on the basis of IGBT's for medium breakdown voltages (600  $V \le v_{Bf} \le 1700 \text{ V}$ ) and switching frequencies (5 kHz $\le f_S \le 40 \text{ kHz}$ ). The most important IGBT-switch configurations of a MC and of the conventional hard switching dc-voltage-link converter are depicted in Table I for comparison purposes. Configurations 1 and 2 show how a back to back arrangement of IGBT's may be used to implement the required bi-directional switch. The two diodes are used to provide the reverse voltage blocking capability. The diodes are also effectively placed in parallel with the IGBT by use of the short at the mid point of the two branches. These arrangements are preferable to the analogous configurations without a short at the mid point as they prevent a possible avalanche breakdown of the IGBT's during the interruption of the reverse current. Furthermore both the common emitter and the common collector configuration allow the use of single modules reducing the costs of assembly substantially. Because the common collector arrangement requires the minimum number of isolated gate drives this switch configuration is the cheapest and also technically preferable implementation of all back-to-back configurations on the basis of conventional PT- or NPT-IGBT's. A comparison of the number of the required semiconductors shows that the matrix converter needs

TABLE I

SWITCH CONFIGURATIONS OF A MATRIX CONVERTER

|                                      | Variant | Switch<br>Configuration | Driver | IGBTs/<br>Diodes/<br>Total |

|--------------------------------------|---------|-------------------------|--------|----------------------------|

| Matrix Converter                     | 1       |                         | 9      | 18 / 18 / 36               |

|                                      | 2       | \$                      | 9      | 18 / 18 / 36               |

|                                      | 3       | <b>\$</b>               | 6      | 18/0/18                    |

| DC-<br>Voltage-<br>Link<br>Converter |         | \$                      | 7      | 12 / 12 / 24               |

6 IGBTs and 6 diodes more than the comparable PWM dc-voltage-link converter if the CCC is used as 4QSW (Table I). In spite of these different numbers of required semiconductors, a detailed investigation of the switch ratings has shown that the installed total switch power of both circuits is generally the same due to the possible reduction of the current ratings of the switches in the matrix converter by one third [4].

The expense of semiconductors can be reduced even more if one uses the capability of NPT-IGBT's to block both forward and reverse voltages. The saved series diodes and the possible reduction of the current ratings of the IGBT's are the reason therefore, that in this case the installed total switch power of the matrix converter can be distinctly lower than that of the dc voltage link converter.

IV. BEHAVIOR OF FOUR-QUADRANT SWITCHES ON THE BASIS OF COMMON COLLECTOR CONFIGURATIONS AND REVERSE BLOCKING NPT-IGBTS

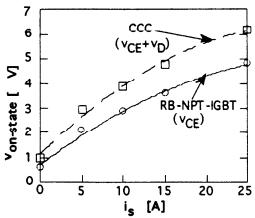

To illustrate the advantages of the matrix converter over the dc voltage link converter, measured on-state and switching losses of CCC's and RB-NPT-IGBT's will now be discussed. The CCC's were realized using the NPT-IGBT BUP 304 (1000V, 25A) and the fast epitaxial diode BYP 103 (1000V, 45A). The 4QSW with RB-NPT-IGBT's used the same IGBT BUP 304 but without additional diodes. In contrast to the CCC a gate voltage of vGE=+15V was applied in the reverse blocking state of the RB-NPT-IGBT to minimize the leakage current and the stationary reverse blocking losses [9], [10].

The measured on-state voltages of both switch arrangements are to be seen in Fig. 2. Because of the additional voltage drop across the series diode the resulting on-state voltage of the CCC is about 40% higher on average than that of the RB-NPT-IGBT.

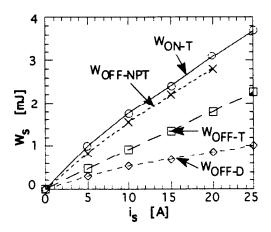

Detailed investigations of the switching losses of 4QSW's showed that nearly all switching losses are caused by the active turn-on transient of the IGBT's (WON-T), the turn-off losses during the reverse recovery process of the diodes (WOFF-D) and the RB-NPT-IGBT's (WOFF-NPT)

Fig. 2: On-state voltages of CCC's and RB-NPT-IGBT's (BUP 304; BYP 103;  $T_j$ =125° C)

respectively and the active turn-off transient of the IGBT's (WOFF-T). Fig. 3 shows the measured switching losses of both types of switch configurations in a hard switching buck converter which was used as a simple equivalent circuit to determine the losses in the MC. Obviously the IGBT turn-on losses WON-T are distinctly higher than the turn-off losses WOFF-T of the IGBT's. Even more important is the fact that the reverse recovery losses of the RB-NPT-IGBT (WOFF. NPT) are drastically higher than those of the fast epitaxial diode (WOFF-D) because of the unfavorable charge carrier distribution and the high carrier lifetime in the NPT-IGBT. However, it must be taken into account that the investigated currently produced NPT-IGBT's are not designed for the passive turn-off transient. A substantial improvement of the poor reverse recovery behavior of the NPT-IGBT appears to be possible by a reduction of the carrier lifetime and an increase in the emitter efficiency.

Fig. 3: Switching losses of CCC's and RB-NPT-IGBT's (BUP 304; BYP 103;  $T_i$ =125° C;  $v_C$ =600V)

# V. A NEW MODEL FOR THE SEMICONDUCTOR LOSS ESTIMATION IN THE MATRIX CONVERTER

A new semiconductor loss model has been developed to determine and to compare the losses in a matrix converter for different switch implementations. The basis of the model is the analytical description of the measured switching losses and on-state voltages at junction temperatures of  $T_j=25^{\circ}$  C and  $T_j=125^{\circ}$ C by the following equations:

$$\begin{split} v_{\text{CE}} = & \left(v_{0\text{T}} + r_{0\text{T}} \cdot i_{\text{S}}^{\text{BconT}}\right) \cdot \left(1 - \frac{125^{\circ}\text{C-T}_{j} \left[^{\circ}\text{C}\right]}{100^{\circ}\text{C}} C_{\text{conT}}\right) \\ v_{D} = & \left(v_{0\text{D}} + r_{0\text{D}} \cdot i_{\text{S}}^{\text{BconD}}\right) - \left(T_{j} \left[^{\circ}\text{C}\right] - 125^{\circ}\text{C}\right) C_{\text{conD}} \\ W_{\text{ONT}} = & \left(A_{\text{ONT}} \cdot i_{\text{S}}^{\text{BONT}}\right) \left(1 - \frac{125^{\circ}\text{C-T}_{j} \left[^{\circ}\text{C}\right]}{100^{\circ}\text{C}} C_{\text{ONT}}\right) \cdot F \\ W_{\text{OFFT}} = & \left(A_{\text{OFFT}} \cdot i_{\text{S}}^{\text{BOFFT}}\right) \left(1 - \frac{125^{\circ}\text{C-T}_{j} \left[^{\circ}\text{C}\right]}{100^{\circ}\text{C}} C_{\text{OFFT}}\right) \cdot F \\ W_{\text{OFFD}} = & \left(A_{\text{OFFD}} \cdot i_{\text{S}}^{\text{BOFFD}}\right) \left(1 - \frac{125^{\circ}\text{C-T}_{j} \left[^{\circ}\text{C}\right]}{100^{\circ}\text{C}} C_{\text{OFFD}}\right) \cdot F \\ F = & \left(1 - \frac{600V - |v_{\text{C}}[V]|}{600V}\right) \end{split}$$

where v<sub>c</sub>: Commutation voltage

is: Switch current

T<sub>j</sub>: Junction temperature v<sub>0</sub>: Bias voltage at T<sub>i</sub>=125° C

$r_0$ : Dynamic resistance at  $T_1$ =125° C

A,B,C: Curve fitted constants at  $T_i=125^{\circ}$  C,

$(v_c = 600V)$

The fitting of the on-state voltages and switching losses for the IGBT BUP 304 and the diode BYP 103 with "Mathematica" subsequently generated the constants given in Table II.

TABLE II

FITTED PARAMETERS FOR LOSS SIMULATION

|                     | BUP 304 | BYP 103  |

|---------------------|---------|----------|

| VOT/D               | 0.6     | 0.4      |

| r0T/D               | 0.72    | 0.18     |

| B <sub>conT/D</sub> | 0.53    | 0.53     |

| C <sub>conT/D</sub> | 0.2     | 0.00365  |

| AONT                | 0.43    |          |

| BONT                | 0.64    | <i>P</i> |

| CONT                | 0.37    |          |

| AOFFT               | 0.1     |          |

| BOFFT               | 0.97    |          |

| COFFT               | 0.27    |          |

| AOFFD               | 0.23    | 0.09     |

| BOFFD               | 0.84    | 0.74     |

| COFFD               | 0.27    | 0.73     |

In addition to this analytical approximation of the occurring losses, the model contains an algorithm which determines the type of each switching transient and distributes the losses to the active semiconductors of the 4QSW's.

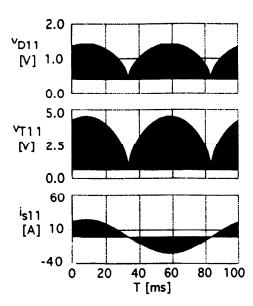

As an example Fig. 4 shows the computed on-state voltages of the active IGBT's and diodes of the switch s<sub>11</sub>.

Fig. 4: Simulated switch current and on-state voltages of a CCC (BUP 304; BYP 103; 480V main;  $i_{omax}$  =25 A;  $f_i$  = 60 Hz;  $f_o$ = 10 Hz; q=0.166;  $f_s$ = 20 kHz;  $T_i$ = 125° C)

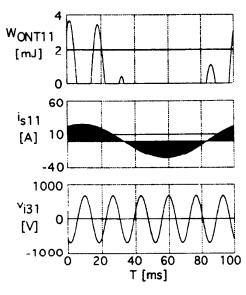

The line-to-line voltage v<sub>131</sub>, the switch current i<sub>s11</sub> and the instantaneous turn-on losses of one IGBT of the switch s<sub>11</sub> are to be seen in Fig. 5.

Because on the one hand the switching and on-state losses are computed at each integration step and on the other hand also the fitted functions closely approximate the measured losses, the developed loss model should describe the semiconductor losses of an actual matrix converter very accurately.

Fig. 5: Simulated line-to-line voltage, switch current and turn-on losses of an IGBT in a CCC (BUP 304; BYP 103; 480 V main; i<sub>omax</sub>= 25 A; f<sub>i</sub>= 60 Hz; f<sub>o</sub>= 10 Hz; q= 0.166; f<sub>s</sub>= 20 kHz; T<sub>i</sub>=125°C)

### VI. LOSS COMPARISON OF A MATRIX CONVERTER WITH COMMON COLLECTOR SWITCH CONFIGURATIONS AND REVERSE BLOCKING NPT-IGBT'S

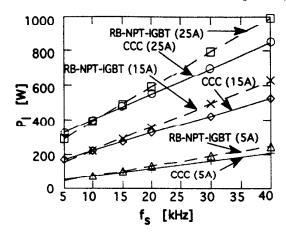

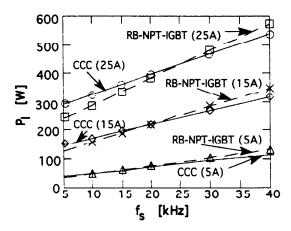

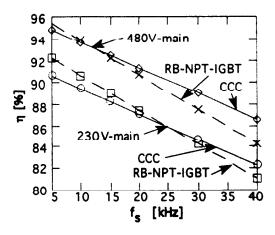

Figures 6 and 7 show the simulated semiconductor losses of a MC as a function of the switching frequency if the MC is operated at an 480V and 230V main (60 Hz) respectively.

Fig. 6: Simulated matrix converter losses for RB-NPT-IGBT's and CCC's (BUP 304; BYP 103; 480V main;  $i_{0max}$ =5A/15A/25A;  $f_{1}$  = 60 Hz;  $f_{0}$  = 30 Hz; q = 0.5;  $\phi_{1}$  = 0°;  $\phi_{0}$  = 30°;  $T_{j}$  = 125° C)

It is obvious that the MC with RB-NPT-IGBT's halves not only the number of the required switches but generates also less losses than MC with conventional CCC's up to crossover switching frequencies of  $f_{SCT} = 6$  kHz ( $i_{Omax} = 5$  A), 10 kHz ( $i_{Omax} = 15$  A), 12 kHz ( $i_{Omax} = 25$ A) [480 V-main] and  $f_{SCT} = 12$ kHz ( $i_{Omax} = 5$  A), 20 kHz ( $i_{Omax} = 15$  A), 25 kHz ( $i_{Omax} = 25$ A) [230V-main] respectively. For  $f_{S} > f_{SCT}$  the excellent reverse recovery behavior of the fast epitaxial diode selected and the resulting low diode turn-off losses WOFF-D are the reason therefore that the CCC realizes lower

Fig. 7: Simulated matrix converter losses for RB-NPT-IGBT's and CCC's (BUP 304; BYP 103; 230V main;  $i_{omax}$ =5A/15A/25A;  $f_i$ =60Hz;  $f_o$ =30Hz; q=0.5;  $\phi_i$ =0 °;  $\phi_o$ =30°;  $T_j$ =125°C)

Fig. 8: Simulated matrix converter efficiency for RB-NPT-IGBT's and CCC's (BUP 304; BYP 103;  $i_{omax}$ =25A;  $f_i$ =60Hz;  $f_o$ =30Hz; q=0.5;  $\phi_i$ =0 °;  $\phi_o$ =30 °;  $T_j$ =125 °C)

losses than RB-NPT-IGBT's despite the additional voltage drop across the diodes. Because of the different average commutation voltages of the two considered mains, the cross-over switching frequencies of a MC at 230 V are approximately twice as much as that of the MC at 480 V.

The resulting efficiency  $\eta$  of the MC with both switch configurations is depicted in Fig. 8 for  $i_{omax} = 25$  A. As expected the converter efficiency goes up with increasing voltage utilization of the switches.

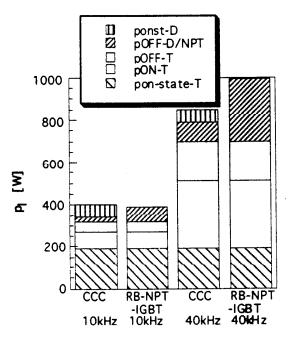

Fig. 9 shows the distribution of the losses of a MC with a

Fig. 9: Loss distribution in a matrix converter for RB-NPT-IGBT's and CCC's (RUP 304; BYP 103: 480V main:  $i_{omax}$ =25A:  $f_i$ =60Hz;  $f_0$ =30Hz; q=0.5;  $\phi_i$ =0 °;  $\phi_0$ =30°;  $T_i$ =125°C)

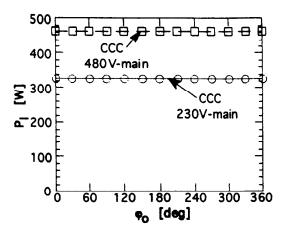

Fig. 10: Simulated matrix converter losses for CCC's (BUP 304; BYP 103;  $i_{oRMS}$ =15A;  $f_{i}$ =60Hz;  $\phi_{i}$ =0 °;  $f_{o}$ =30Hz; q=0.5;  $f_{s}$ =20kHz;  $T_{i}$ =125 ° C)

480V main supply for switching frequencies of  $f_S = 10 \text{ kHz}$  and  $f_S = 40 \text{ kHz}$ . The on-state losses are roughly so high as the switching losses at  $f_S = 10 \text{ kHz}$  (CCC:  $P_S = 0.37 \cdot P_I$ ; RB-NPT-IGBT::  $P_S = 0.51 \cdot P_I$ ). However the switching losses dominate clearly at  $f_S = 40 \text{ kHz}$  (CCC:  $P_S = 0.7 \cdot P_I$ ; RB-NPT-IGBT:  $P_S = 0.81 \cdot P_I$ ). Although the simulations show, that both switch arrangements can be operated at switching frequencies of  $f_S > 40 \text{ kHz}$  the substantial switching losses and low converter efficiencies at high switching frequencies limit the switching frequency to about 20 kHz - 25 kHz.

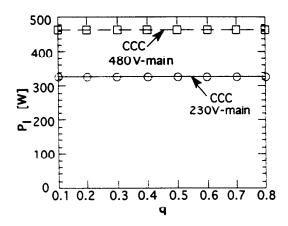

The dependence of the converter losses of the phase shift  $\phi_0$  at the output and the voltage ratio  $q=v_0/v_1$  can be seen in the Figures 10 and 11. In contrast to the PWM-voltage source inverter, where the losses are strongly dependent on the modulation index and the phase shift  $\phi_0$  due to the different on-state voltages of IGBT and diode [11], the losses of the MC are independent of the phase shift  $\phi_0$  and the voltage ratio q because of the symmetrical structure of the 4QSW's.

Fig. 11: Simulated matrix converter losses for CCC's (BUP 304; BYP 103;  $i_0$ RMS=15A:  $f_i$ =60Hz;  $f_0$ =30Hz; ;  $f_s$ =20kHz;  $\phi_i$ =0° : $\phi_0$ =30°;  $T_i$ =125° C)

# VII. AN OPTIMIZED PULSE PATTERN TO MINIMIZE THE INPUT CURRENT HARMONICS

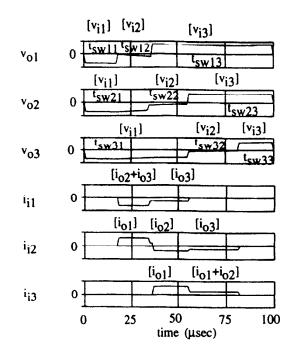

Each output phase of a three-phase to three-phase matrix converter is connected to each input phase for a certain time period during each switching interval where each time period is determined so that each output voltage is to be an average voltage of three input voltage pulses. For example, the output phase 1 is connected to the input phase 1 for a time interval  $t_{sw11}$ , to the input phase 2 for a time interval  $t_{sw12}$ , and to the input phase 3 for a time interval  $t_{sw13}$ , where  $t_{sw11} + t_{sw12} + t_{sw13} = T_s$  and the switching interval  $T_s = 1/f_s$  ( $f_s$  is the switching frequency). When the switching frequency  $f_s$  is 10 kHz the switching interval  $T_s = 100$  µsec. The output phase 2 is connected to the input phase 1 for a time interval  $t_{sw23}$ , and to the input phase 3 for a time interval  $t_{sw23}$ , where  $t_{sw21} + t_{sw22} + t_{sw23} = T_s$ . The output phase 3 is connected to the input phase 1 for a time interval  $t_{sw31}$ , to the input phase 2 for a time interval  $t_{sw31}$ , and to the input phase 3 for a time interval  $t_{sw31}$ , to the input phase 2 for a time interval  $t_{sw31}$ , and to the input phase 3 for a time interval  $t_{sw31}$ , where  $t_{sw31} + t_{sw32} + t_{sw33} = T_s$ . The three phase output voltages can be described

$$v_{01} = v_{i1} * \frac{t_{sw11}}{T_s} + v_{i2} * \frac{t_{sw12}}{T_s} + v_{i3} * \frac{t_{sw13}}{T_s}$$

$$v_{02} = v_{i1} * \frac{t_{sw21}}{T_s} + v_{i2} * \frac{t_{sw22}}{T_s} + v_{i3} * \frac{t_{sw23}}{T_s}$$

$$v_{03} = v_{i1} * \frac{t_{sw31}}{T_s} + v_{i2} * \frac{t_{sw32}}{T_s} + v_{i3} * \frac{t_{sw33}}{T_s}$$

There is no restriction on the sequence of the three time intervals, that is, the output phase 1 can be connected to the input phase 2 first and then phase 3 and phase 1, or to the input phase 3 first and then phase 1 and phase 2. The average value of the output voltage  $v_{O1}$  remains the same in either switching sequence combination. It can be shown that there exist 216 different switching sequence combinations for a nine-switch three-phase to three-phase matrix converter to produce a specific three-phase output voltage. The matrix converter input current characteristics depends on the switching sequence combinations while the output current characteristics are not significantly affected by the change of the switching sequence combinations.

A switching sequence combination was developed to obtain a balanced three-phase input current characteristics of the matrix converter (the combination #1). With the combination #1, the output phase 1 is connected to the input phase 1 first and phase 2 next and then phase 3, the output phase 2 is connected to the input phase 2 first and phase 3 next and then phase 1, and the output phase 3 is connected to the input phase 3 is connected to the input phase 3 first and phase 1 next and then phase 2. The three phase input currents are well balanced with combination #1.

To reduce the total rms value of the input currents another switching sequence combination was developed (combination #2). With the combination #2 the output phase 1 is connected to the input phase 1 first and phase 2 next and then phase 3, which is same as the combination #1, however, both the output phase 2 and phase 3 are connected to the input phase 1 first and phase 2 next and then phase 3 in the same manner as the output phase 1, which is illustrated in Fig. 12. As shown in Fig. 12, during the time period of  $t_{SW1}$  the input phase 1 is connected to all the output phases, that means that  $t_{11} = t_{01} + t_{02} + t_{03} = 0$ . Also  $t_{11} = 0$  during the

Fig. 12: Illustration of the switching scheme #2 for one period of the switching sequence

time period  $t_1 = T_S - t_{SW31}$  because no output phases are connected to the input phase 1. The input phase 2 current  $i_{12} = 0$  during the time periods  $t_2 = t_{SW11}$  and  $t_3 = t_{SW33}$  because no output phases are connected to the input phase 2. During the time period  $t_{SW33}$  the input phase 3 is connected to all the output phases, which means  $i_{13} = 0$ , and also  $i_{13} = 0$  during the time period of  $t_4 = T_S - t_{SW13}$ . The simulation result shows that the rms current of the input phase 1 with the combination #2 is 39 % less than the one with the combination #1. The rms values of the input phase 2 and 3 currents with the combination #2 are 17 % and 39 % less than the ones with the combination #1, respectively. The rms current of the input phase 2 is 34 % larger than the input phases 1 and 3.

The switching sequence combination #3 is defined to have all the three phase outputs connected to the input phase 2 first and phase 3 next and then phase 1. The rms currents of the input phase 1, 2 and 3 with the combination #3 are 39 %, 39 % and 17 % less than the sequence with combination #1, respectively. All the three-phase outputs are connected to the input phase 3 first and phase 1 next and the phase 2 with the switching sequence combination #4. The rms values of the input phase 1, 2 and 3 currents with the combination #4 are 17 %, 39 % and 39 % less than the ones with the combination #1, respectively.

The switching sequence combination #5 was developed to obtain the minimum and balanced three phase input currents. The combination #5 uses the three switching sequence combinations #2, #3 and #4. The switching sequence combinations #2, #3, and #4 create less input harmonic currents, though one input phase has more harmonic current than the other two phases while each phase current has the same fundamental component. The switching sequence combination #5 alternates the combinations #2, #3 and #4 every sampling period. The rms values of the input currents

TABLE III

RMS VALUES OF THREE-PHASE INPUT CURRENTS FOR SIX

SWITCHING SEQUENCE COMBINATIONS

| switching<br>sequence<br>combination | rms value of input phase 1 current (%) | rms value of<br>input phase 2<br>current<br>(%) | rms value of input phase 3 current (%) |

|--------------------------------------|----------------------------------------|-------------------------------------------------|----------------------------------------|

| #1                                   | 100                                    | 100                                             | 100                                    |

| #2                                   | 61                                     | 83                                              | 61                                     |

| #3                                   | 61                                     | 61                                              | 83                                     |

| #4                                   | 83                                     | 61                                              | 61                                     |

| #5                                   | 69                                     | 69                                              | 69                                     |

| #6                                   | 69                                     | 69                                              | 69                                     |

are well balanced and 31 % less than the ones with the combination #1. Because of the alternation of the three switching sequence combinations, this scheme creates low harmonic frequency components, that is, every one third of the switching frequency.

The lower frequency components of the harmonic currents are harmful because the harmonic currents are amplified near the frequency of the resonance between the filter capacitance and the main source inductances. To avoid the spread of harmonic current components, the switching scheme combination # 6 has been developed. Combination #6 alternates the three switching sequence combinations #2, #3, and #4 with low frequency, that is, for example, applying the switching sequence combination # 2 for 50 milliseconds and then the # 3 for the next 50 milliseconds and the # 4 for the next 50 milliseconds and then repeating the sequence. In this manner the lowest major harmonic current components are limited in the frequency range of 100 Hz below the switching frequency. The developed switching sequence combination #6 is an optimum switching sequence combination for the threephase to three-phase matrix converter to obtain the minimum and balanced three-phase input current characteristics. The rms values of the input currents with the combination #6 are well balanced and 31 % less than the ones with the combination #1.

Table III summarizes the rms values of three phase input currents for the six switching sequence combinations that are described in this section, where the rms values are relative values to the one with the switching sequence combination #1

#### VIII. CONCLUSIONS

This paper compares IGBT-MC's with conventional common collector switch configurations and reverse blocking NPT-IGBT arrangements. It is shown that by the use of reverse blocking NPT-IGBT's the number of the required semiconductors can be halved in comparison to conventional switch implementations. A new semiconductor loss model was used to compute the losses in a matrix converter for conventional switches and reverse blocking NPT-IGBT's. The comparison of the converter losses shows that reverse blocking NPT-IGBT's realize lower losses up to cross-over switching frequencies of  $f_{SCr} = 6 \text{ kHz} - 25 \text{ kHz}$ . In contrast to PWM voltage source inverters the losses of a matrix converter are independent of the phase shift at the output and the voltage transfer ratio. In addition a new pulse pattern is proposed which minimizes the input current harmonics. This work suggests that matrix converters bear careful consideration as a possible alternative to a conventional dc link PWM rectifier/inverter.

#### **REFERENCES**

- [1] L. Gyugi and B. Pelly, Static Power Frequency Changers. New York: Wiley, 1976

- [2] M.G.B. Venturini and A. Alesina, "Solid state power conversion: A fourier analysis approach to generalized transformer synthesis", *IEEE Trans. Circuits Syst.*, vol. CAS-28, no. 4, pp. 319-330, 1981

- [3] M G B. Venturini and A. Alesina, "Intrinsic amplitude limits and optimum design of 9-switches direct PWM-acac converters", Conf. Rec. IEEE-PESC, 1988, pp. 1284-1291

- [4] T. Matsuo, S. Bernet, S. Colby, T.A. Lipo, "Application of the matrix converter to field oriented induction motor drives", to be published

- [5] L. Huber and D. Borojevic, "Space vector modulated three-phase to three-phase matrix converter with input power factor correction", *IEEE Trans. Ind. Applicat.*, vol. 31, no. 6, pp. 1234-1246, 1996

- [6] D. G. Holmes and T.A. Lipo, "Implementation of a controlled rectifier using ac-ac matrix converter theory", *IEEE Trans. Power Electron.*, vol. 7, no. 1, pp. 240-250, 1992

- [7] P.W. Wheeler and D.A. Grant,"A low loss matrix converter for ac variable-speed drives", Conf. Rec. EPE, 1993, pp. 27-32

- [8] J. Petzoldt, S. Bernet., T. Reimann, "Comparison of power converters with dc-and ac-link", *Conf. Rec. EPE*, 1993, vol. 3, pp. 189-195

- [9] S. Bernet and J. Petzoldt," AC-link converters with MCTs and reverse blocking NPT-IGBTs", Conf. Rec. IEEE-PESC, 1995, pp. 1258-1264

- [10] S. Bernet, T. Reimann, T. Taleb, J. Petzoldt, "Special effects of IGBTs in ZCS and ZVS applications", Conf. Rec. PCIM, 1994, pp. 203-217

- [11] F. Blaabjerg, U. Jaeger, S. Munk-Nielsen, J.K. Pedersen, "Power losses in PWM-VSI inverter using NPT or PT IGBT devices", *IEEE Trans. Power Electron.*, vol. 10, no. 3, pp. 358-367, 1992